晶体管发展历史

作者|蒋思莹 来源|半导体行业观察(ID:icbank)

得益于晶体管的出现,才有了如今电子产品的昌盛。因此,晶体管也被誉为20世纪最伟大发明,它的出现为集成电路、微处理器以及计算机内存的产生奠定了基础。自晶体管诞生到如今,经过了几十年的发展,晶体管也发生了翻天覆地的变化。

晶体管的诞生

在晶体管诞生之前,放大电信号主要是通过真空电子管,但由于真空管制作困难、体积大、耗能高且使用寿命短,使得业界开始期望电子管替代品的出现。1945年秋天,贝尔实验室正式成立了以肖克利为首的半导体研究小组,成员有布拉顿、巴丁等人,开始对包括硅和锗在内的几种新材料进行研究。

1947年贝尔实验室发表了第一个以锗半导体做成的点接触晶体管。但由于点接触晶体管的性能尚不佳,肖克利在点接触晶体管发明一个月后,提出了使用p-n 结面制作接面晶体管的方法,称为双极型晶体管。当时巴丁、布拉顿主要发明半导体三极管;肖克利则是发明p-n 二极管,他们因为半导体及晶体管效应的研究获得1956年诺贝尔物理奖。

晶体管因为有以下的优点,因此可以在大多数应用中代替真空管:

没有因加热阴极而产生的能量耗损,应用真空管时产生的橙光是因为加热造成,有点类似传统的灯泡。

体积小,重量低,因此有助于电子设备的小型化。

工作电压低,只要用电池就可以供应。

在供电后即可使用,不需加热阴极需要的预热期。

可透过半导体技术大量的生产。

放大倍数大。

平面晶体管

平面工艺是60年代发展起来的一种非常重要的半导体技术。该工艺是在Si半导体芯片上通过氧化、光刻、扩散、离子注入等一系列流程,制作出晶体管和集成电路。凡采用所谓平面工艺来制作的晶体管,都称为平面晶体管。

平面晶体管的基区一般都是采用杂质扩散技术来制作的,故其中杂质浓度的分布不均匀(表面高,内部低),将产生漂移电场,对注入到基区的少数载流子有加速运动的良好作用。所以平面晶体管通常也是所谓漂移晶体管。这种晶体管的性能大大优于均匀基区晶体管。

传统的平面型晶体管技术,业界也存在两种不同的流派,一种是被称为传统的体硅技术(Bulk SI),另外一种则是相对较新的绝缘层覆硅(SOI)技术。平面Bulk CMOS和FD-SOI曾在22nm节点处交锋了。其中,Bulk CMOS是最著名的,也是成本最低的一种选择,因此它多年来一直是芯片行业的支柱。但随着技术的推进,Bulk CMOS晶体管容易出现一种被称为随机掺杂波动的现象。Bulk CMOS晶体管也会因此可能会表现出与其标称特性不同的性能,并且还可能在阈值电压方面产生随机差异。解决这个问题的一种方法是转向完全耗尽的晶体管类型,如FD-SOI或FinFET。

Bulk CMOS与FD-SOI两者的区别在于后者在硅基体顶部增加了一层埋入式氧化物(BOX)层,而BOX上则覆有一层相对较薄的硅层。该层将晶体管与衬底隔离,从而阻断器件中的泄漏。Intel是体硅技术的坚定支持者,而IBM/AMD则是SOI技术的绝对守护者。

FinFet晶体管

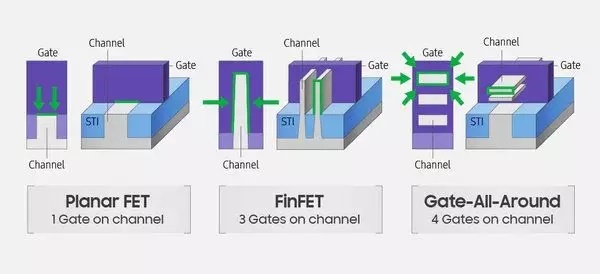

平面晶体管主导了整个半导体工业很长一段时间。但随着尺寸愈做愈小,传统的平面晶体管出现了短通道效应,特别是漏电流,这类使得元件耗电的因素。尤其是当晶体管的尺寸缩小到25nm以下,传统的平面场效应管的尺寸已经无法缩小。在这种情况下,FinFET出现了。FinFET也被称为鳍式场效应晶体管,这是一种立体的场效应管。FinFET的主要是将场效应管立体化。

第一种FinFET晶体管类型称为“耗尽型贫沟道晶体管”或“ DELTA”晶体管,该晶体管由日立中央研究实验室的Digh Hisamoto,Toru Kaga,Yoshifumi Kawamoto和Eiji Takeda于1989年在日本首次制造。但目前所用的FinFet晶体管则是由加州大学伯克利分校胡正明教授基于DELTA技术而发明,属于多闸极电晶体。

多闸极晶体管的载子通道受到接触各平面的闸极控制。因此提供了一个更好的方法可以控制漏电流。由于多闸极晶体管有更高的本征增益和更低的沟道调制效应,在类比电路领域也能够提供更好的效能。如此可以减少耗电量以及提升芯片效能。立体的设计也可以提高晶体管密度,进而发展需要高密度晶体管的微机电领域。

与平面CMOS(互补金属氧化物半导体)技术相比,FinFET器件具有明显更快的开关时间和更高的电流密度。FinFET是一种非平面晶体管或“ 3D”晶体管。它是现代纳米电子半导体器件制造的基础。

2011年,英特尔将之用于22nm工艺的生产,正式走向商业化。从2014年开始,14nm(或16nm)的主要代工厂(台积电,三星,GlobalFoundries)开始采用FinFET设计。在接下来的发展过程中,FinFET也成为了14 nm,10 nm和7 nm工艺节点的主要栅极设计。

GAA晶体管

而当先进工艺发展到了7nm阶段,并在其试图继续向下发展的过程中,人们发现,FinFET似乎也不能满足更为先进的制程节点。于是,2006年,来自韩国科学技术研究院(KAIST)和国家nm晶圆中心的韩国研究人员团队开发了一种基于全能门(GAA)FinFET技术的晶体管,三星曾表示,GAA技术将被用于3nm工艺制程上。

GAA全能门与FinFET的不同之处在于,GAA设计围绕着通道的四个面周围有栅极,从而确保了减少漏电压并且改善了对通道的控制,这是缩小工艺节点时的基本步骤,使用更高效的晶体管设计,再加上更小的节点尺寸,和5nm FinFET工艺相比能实现更好的能耗比。

GAA 技术作为一款正处于预研中的技术,各家厂商都有自己的方案。比如 IBM 提供了被称为硅纳米线 FET (nanowire FET)的技术,实现了 30nm 的纳米线间距和 60nm 的缩放栅极间距,该器件的有效纳米线尺寸为 12.8nm。此外,新加坡国立大学也推出了自己的纳米线 PFET,其线宽为 3.5nm,采用相变材料 Ge2Sb2Te5 作为线性应力源。

另据据韩媒Business Korea的报道显示,三星电子已经成功攻克了3nm和1nm工艺所使用的GAA (GAA即Gate-All-Around,环绕式栅极)技术,正式向3nm制程迈出了重要一步,预计将于2022年开启大规模量产。

结语

从平面晶体管走到GAA晶体管,代工厂的研发投入越来越高。在这个过程中,格芯和联电接连放弃了14nm以下先进制程的研究,英特尔虽然公布了其7nm计划,但其已在10nm工艺节点上停留了很久。而三星也在7nm节点处落后于台积电的发展,在这种情况下,台积电几乎包揽了市场上所有7nm的生意。

但先进工艺不会因为玩家变少而停滞不前,按照三星早早公布GAA晶体管的最近状态中看,其势要在3nm节点处,与台积电一争高下。而台积电方面除了有消息透露其将采用EUV光刻外,并无新的杀手锏。在3nm节点处,新的晶体管会改变现有代工厂的市场地位吗?晶体管未来还会发生怎样的变化,都值得大家共同期待。

编者按:本文转载自微信公众号:半导体行业观察(ID:icbank),作者:蒋思莹

品牌、内容合作请点这里:寻求合作 ››

前瞻经济学人

专注于中国各行业市场分析、未来发展趋势等。扫一扫立即关注。